# LOGIC DEVICES

#### **Unit Structure**

- 1.1 Introduction

- 1.2 Tristate devices

- 1.3 Buffers

- 1.4 Encoder

- 1.5 Decoder

- 1.6 Latches

- 1.7 Summary

- 1.8 Review Questions

- 1.9 Reference

# **1.0 OBJECTIVES**

After studying this chapter you should be able to

- Understand the working of tri state devices

- Explain the use of buffer in electronics

- Describe the use of encoder and decoder in 8085

- Understand the working of Latch

# **1.1 INTRODUCTION**

The chapter reviews logic theory of encoder and decoder. It discusses the working of tristate devices and latch. These logic devices play an important role in 8085 microprocessor. In order to separate the low order address bus and data bus, latch IC is used.

# **1.2 TRI-STATE DEVICES**

Tri-state logic devices have three states:

- 1) Logic 1 or Low

- 2) Logic 0 or High

- 3) High impedance

A tri-state logic device has a extra input line called **Enable**. When this line is active (Enabled), a tri-state device functions in the same way as ordinary logic devices. When this line is not active(disabled), the logic device goes into a high impedance state, as if it is disconnected from the system and practically no current is drawn from the system.

# **1.3 BUFFER**

A **Digital Buffer** is a single input device that does not invert or perform any type of logical operation on its input signal. In other words, the logic level of the output is same as that of the input. The buffer is a logic circuit that amplifies the current or power. The buffer is used primarily to increase the driving capability of a logic circuit. It is also known as driver.

| Symbol                          | Truth Table        |               |

|---------------------------------|--------------------|---------------|

|                                 | А                  | Q             |

|                                 | 0                  | 0             |

| A Tri-state Buffer              | 1                  | 1             |

| Boolean Expression <b>Q = A</b> | Read as <b>A</b> g | ives <b>Q</b> |

## 1.3.1 Tri-state Buffer

A Tri-state Buffer can be thought of as an input controlled switch which has an output that can be electronically turned "ON" or "OFF" by means of an external "Enable" signal input. This Enable signal can be either a logic "0" or a logic "1" type signal. When Enable line is low (logic '0'), the circuit functions as a buffer. When Enable line is high (logic '1'), its output produces an open circuit condition that is neither "High" nor "low", but instead gives an output state of very high impedance, **high-Z**, or more commonly Hi-Z.

Then this type of device has two logic state inputs, "0" or a "1" but can produce three different output states, "0", "1" or "Hi-Z" which is why it is called a "3-state" device.

There are two different types of Tri-state Buffer, one whose output is controlled by an "Active-HIGH" Enable signal and the other which is controlled by an "Active-LOW" Enable signal, as shown below

| 1.3.1 | Active | "HIGH" | <b>Tri-state</b> | Buffer |

|-------|--------|--------|------------------|--------|

|       |        |        |                  |        |

| ľ | Symbol | Truth Table |

|---|--------|-------------|

|   | ,      |             |

| Enable                                           | Enable | А | Q    |

|--------------------------------------------------|--------|---|------|

|                                                  | 1      | 0 | 0    |

|                                                  | 1      | 1 | 1    |

|                                                  | 0      | 0 | Hi-Z |

| Tri-state Buffer                                 | 0      | 1 | Hi-Z |

| Read as Output = Input if Enable is equal to "1" |        |   |      |

An **Active-high** Tri-state Buffer is activated when a logic level "1" is applied to its "**enable**" control line and the data passes through from its input to its output. When the enable control line is at logic level "0", the buffer output is disabled and a high impedance condition, Hi-Z is present on the output.

### 1.3.2 Active "LOW" Tri-state Buffer

| Symbol                                                      | Truth              | Fable |      |   |

|-------------------------------------------------------------|--------------------|-------|------|---|

|                                                             | Enab<br>le         | A     |      | Q |

|                                                             | t <mark>ı</mark> O | 0     |      | 0 |

| Tri-state Buffer                                            | 0                  | 1     |      | 1 |

|                                                             | 1                  | 0     | Hi-Z |   |

|                                                             | 1                  | 1     | Hi-Z |   |

| Read as Output = Input if Enable is <b>NOT</b> equal to "1" |                    |       |      |   |

An **Active-low** Tri-state Buffer is the opposite to the above, and is activated when a logic level "0" is applied to its "**enable**" control line. The data passes through from its input to its output. When the enable control line is at logic level "1", the buffer output is disabled and a high impedance condition, Hi-Z is present on the output.

# **1.4 ENCODER**

The encoder is a logic circuit that provides the appropriate code (binary, BCD, etc.) as output for each input signal.

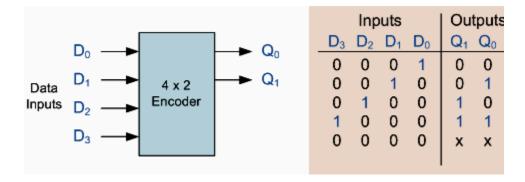

#### 1.4.1 Binary Encoder

A binary encoder, is a multi-input combinational logic circuit that converts the logic level "1" data at its inputs into an equivalent binary code at its output. Generally, digital encoders produce outputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines. An "n-bit" binary encoder has 2<sup>n</sup> input lines and n-bit output lines with common types that include 4-to-2, 8-to-3 and 16-to-4 line configurations. The output lines of a digital

encoder generate the binary equivalent of the input line whose value is equal to "1" and are available to encode either a decimal or hexadecimal input pattern to typically a binary or B.C.D. output code.

#### 1.4.24-to-2 Bit Binary Encoder

One of the main disadvantages of standard digital encoders is that they can generate the wrong output code when there is more than one input present at logic level "1". For example, if we make inputs  $D_1$  and  $D_2$  HIGH at logic "1" at the same time, the resulting output is neither at "01" or at "10" but will be at "11" which is an output binary number that is different to the actual input present. Also, an output code of all logic "0"s can be generated when all of its inputs are at "0" or when input  $D_0$  is equal to one.

One simple way to overcome this problem is to "Prioritise" the level of each input pin and if there was more than one input at logic level "1" the actual output code would only correspond to the input with the highest designated priority. Then this type of digital encoder is known commonly as a **Priority Encoder** or **P-encoder** for short.

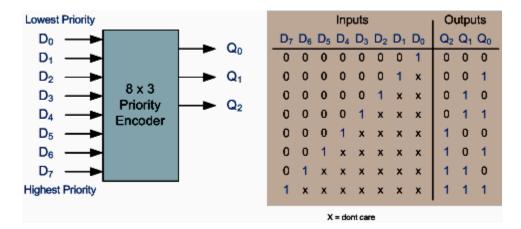

#### **1.4.2Priority Encoder**

The Priority Encoder solves the problems mentioned above by allocating a priority level to each input. The *priority encoders* output corresponds to the currently active input which has the highest priority. So when an input with a higher priority is present, all other inputs with a lower priority will be ignored. The priority encoder comes in many different forms with an example of an 8input priority encoder along with its truth table shown below.

#### 8-to-3 Bit Priority Encoder

Priority encoders are available in standard IC form and the TTL 74LS148 is an 8-to-3 bit priority encoder which has eight active LOW (logic "0") inputs and provides a 3-bit code of the highest ranked input at its output. Priority encoders output the highest order input first for example, if input lines "D2", "D3" and "D5" are applied simultaneously the output code would be for input "D5" ("101") as this has the highest order out of the 3 inputs. Once input "D5" had been reMOVed the next highest output code would be for input "D3" ("011"), and so on.

### **1.5 DECODER**

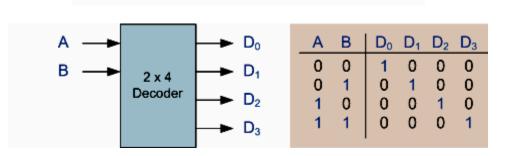

A **Decoder** is the exact opposite to that of an "Encoder". It is basically, a combinational type logic circuit that converts the binary code data at its input into an equivalent decimal code at its output. **Binary Decoders** have inputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines, and a n-bit decoder has 2<sup>n</sup> output lines. Therefore, if it receives n inputs (usually grouped as a binary or Boolean number) it activates one and only one of its 2<sup>n</sup> outputs based on that input with all other outputs deactivated. A decoders output code normally has more bits than its input code and practical binary decoder circuits include, 2-to-4, 3-to-8 and 4-to-16 line configurations.

A binary decoder converts coded inputs into coded outputs, where the input and output codes are different and decoders are available to "decode" either a Binary or BCD (8421 code) input pattern to typically a Decimal output code. An example of a 2-to-4 line decoder along with its truth table is given below.

#### 1.5.1 2-to-4 Binary Decoder

In this simple example of a 2-to-4 line binary decoder, the binary inputs A and B determine which output line from D0 to D3 is "HIGH" at logic level "1" while the remaining outputs are held "LOW" at logic "0" so only one output can be active (HIGH) at any one time. Therefore, whichever output line is "HIGH" identifies the binary code present at the input, in other words it "de-codes" the binary input and these types of binary decoders are commonly used as **Address Decoders** in microprocessor memory applications.

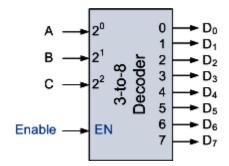

Some binary decoders have an additional input labelled "Enable" that controls the outputs from the device. This allows the decoders outputs to be turned "ON" or "OFF". The logic diagram of the basic decoder is identical to that of the basic demultiplexer. Therefore, one can say that a demultiplexer is a decoder with an additional data line that is used to enable the decoder. An alternative way of looking at the decoder circuit is to regard inputs A, B and C as address signals. Each combination of A, B or C defines a unique address which can access a location having that address.

### 1.6 LATCHES

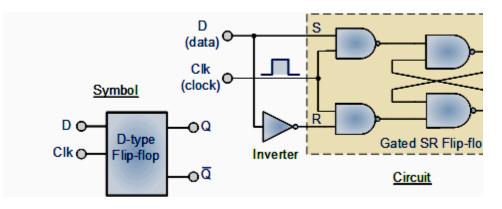

#### The D flip-flop:

The **D** flip-flop is by far the most important of the clocked flip-flops as it ensures that inputs S and R are never equal to one at the same time. D-type flip-flops are constructed from a gated SR flipflop with an inverter added between the S and the R inputs to allow for a single D (data) input. This single data input D is used in place of the "set" signal, and the inverter is used to generate the complementary "reset" input thereby making a level-sensitive Dtype flip-flop from a level-sensitive RS-latch as now S = D and R = notD as shown.

#### D flip-flop Circuit

A simple SR flip-flop requires two inputs, one to "SET" the output and one to "RESET" the output. By connecting NOT gate to the SR flip-flop one can "SET" and "RESET" the flip-flop using just one input as now the two input signals are complements of each other. This complement avoids 'forbidden state' in the SR latch when both inputs are LOW, since that state is no longer possible.

Thus the single input is called the "DATA" input. If this data input is HIGH the flip-flop would be "SET" and when it is LOW the flip-flop would be "RESET". However, this would be rather pointless since the flip-flop's output would always change on every data input. To avoid this an additional input called the "CLOCK" or "ENABLE" input is used to isolate the data input from the flip-flop after the desired data has been stored. The effect is that D is only copied to the output Q when the clock is active. This forms the basis of a **D flip-flop**.

The **D** flip-flop will store and output whatever logic level is applied to its data terminal so long as the clock input is HIGH. Once the clock input goes LOW the "set" and "reset" inputs of the flip-flop are both held at logic level "1" so it will not change state and store whatever data was present on its output before the clock transition occurred. In other words the output is "latched" at either logic "0" or logic "1".

#### Truth Table for the D Flip-flop

| Clk          | D | Q | Q | Description         |

|--------------|---|---|---|---------------------|

| ↓ » 0        | Х | Q | Q | Memory<br>no change |

| ↑ <b>» 1</b> | 0 | 0 | 1 | Reset Q » 0         |

| ↑ » 1        | 1 | 1 | 0 | Set Q » 1           |

Note: ↓ and ↑ indicates direction of clock pulse as it is assumed D flip-flops are edge triggered

## 1.7 SUMMARY

- A tri-state logic device has a extra input line called Enable. When this line is active (Enabled), a tri-state device functions in the same way as ordinary logic devices. When this line is not active(disabled), the logic device goes into a high impedance state, as if it is disconnected from the system and practically no current is drawn from the system.

- A Digital Buffer is a single input device in which the logic level of the output is same as that of the input. The buffer is a logic circuit that amplifies the current or power. The buffer is used primarily to increase the driving capability of a logic circuit.

- The Digital Encoder is a combinational circuit that generates a specific code at its outputs such as binary or BCD in response to one or more active inputs. There are two main types of digital encoder. The Binary Encoder and the Priority Encoder.

- The Binary Encoder converts one of 2<sup>n</sup> inputs into an n-bit output. Then a binary encoder has fewer output bits than the input code. Binary encoders are useful for compressing data and can be constructed from simple AND or OR gates.

- The Priority Encoder is another type of combinational circuit similar to a binary encoder, except that it generates an output code based on the highest prioritised input.

- A Decoder is a combinational type logic circuit that converts the binary code data at its input into an equivalent decimal code at its output.

- There are two different types of Tri-state Buffer, one whose output is controlled by an "Active-HIGH" Enable signal and the other which is controlled by an "Active-LOW" Enable signal.

# **1.8 REVIEW QUESTIONS**

- 1. What do you mean by tri-state devices?

- 2. With the help of a neat symbol explain tri-state buffer.

- 3. State function of buffer.

- 4. Explain different types of encoder.

- 5. With the help of neat block diagram explain 4 to 2 encoder.

- 6. What do you mean by priority encoder?

- 7. With the help of neat block diagram explain 8 to 3 encoder.

- 8. Explain decoder in detail.

- 9. With the help of neat block diagram explain 3 to 8 decoder.

- 10. Explain the working of D flipflop.

# **1.9 REFERENCE**

- Microprocessor Architecture, Programming, and Applications With the 8085 by Ramesh Gaonkar, Publisher: Prentice Hall

- Digital Principles and application by Malvino and Leach, Publisher: McGraw-Hill

# **MEMORY**

## **Unit Structure**

- 1.1 Introduction

- 1.2 Memory

- 1.3 Random Access Memory (RAM)

- 1.4 Read Only Memory (ROM)

- 1.5 Nonvolatile RAM (NVRAM)

- 1.6 Memory Interfacing

- 1.7 Summary

- 1.8 Review Questions

- 1.9 Reference

# 2.0 OBJECTIVES

After studying this chapter you should be able to

- Understand the different types of memory used in 8085

- Distinguish between SRAM & DRAM

- Understand different types ROM

- Understand the different technique of memory interfacing

# **1.6 INTRODUCTION**

Many types of memory devices are available for use in modern computer systems. You must be aware of the differences between them andunderstand how to use each type effectively. As you are reading, try to keep in mind that thedevelopment of these devices took several decades and that there are significant physical differences in the underlying hardware. The names of the memory types frequently reflect the

historical nature of the development process and are often more confusing than insightful.

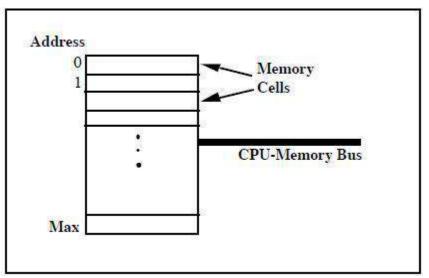

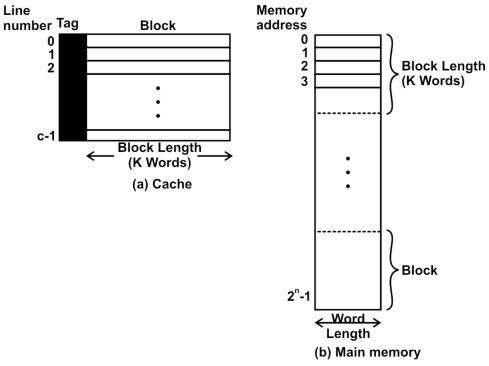

# 1.2 MEMORY

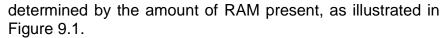

Memory is the storage device which can be used to store monitor program, users program or users data.So memory is an important component of the microprocessor based system, which will allow you to store program and data. The memory consists of the thousands of memory cells arranged to store data. Each memory cell is capable of storing 1 bit of the data. Hence, to use memory to store programs or data of user or system, memory must be interfaced with microprocessor properly, so that it can be accessed while reading or writing data or program from/to it . In the same way, input and output devices are also required to read or write data out from the microprocessor using input device such as keyboard or output device using console.

So, these devices must be interface properly with the microprocessor so that user can read data from input device and write data to the output device

# 1.3 RANDOM ACCESS MEMORY (RAM)

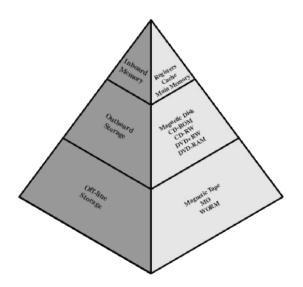

Random accessmeans that the stored data can be accessed in any order, which is in contrast to the morerestricted access provided by other memory systems, such as tape and disk drive. Theaccess time to any piece of data stored on in RAM is essentially the same.

RAM is normally used in computer systems for main memory or primary storage. This iswhere running programs and the data they use are stored. Moving data from primarystorage to the processor requires only a few cycles, although retrieving data from a harddrive can take considerable longer. For this reason, modern operating systems runprimarily in RAM, and as they load and run additional applications, they move theseprograms and their data into RAM for faster processing.

RAM can be categorized as volatile or non-volatile. Volatile means that all data is lostwhen the chip is powered down. Most computers incorporate two types of volatile RAM: static and dynamic. Althoughboth types require constant electrical current to function, they have some important differences.

#### 1.3.1 Dynamic RAM (DRAM)

Dynamic RAM is less expensive, and therefore it is the most widely used.

When a computer is said to have 512 megabytes or one gigabyte of RAM, the specification refers to dynamic RAM (DRAM). DRAM stores each bit of information in a separate capacitor on the integrated circuit. The DRAM chip requires only one transistor and one capacitor for each bit of storage. This makes it both cheap and space efficient. One disadvantage with using capacitors for storage is that they gradually dissipate their charge, so the charge must be refreshed regularly (current specifications are for there fresh to

occur every 64 milliseconds or less). This refresh requirement is what makesthis technology dynamic.

#### 1.3.2 DRAM controller

The DRAM controller is an extra piece of hardwareplaced between the processor and the memory chips. Its main purpose is to perform the refresh operations required to keep your data alive in the DRAM.

Almost all DRAM controllers require a short initialization sequence that consists ofone or more setup commands. The setup commands tell the controller about the hardware interface to the DRAM and how frequently the data there must berefreshed. If the DRAM in your system does not appear to be workingproperly, it could be that the DRAM controller either is not initialized or has beeninitialized incorrectly.

#### 1.3.3 Static RAM (SRAM)

Static RAM (SRAM) has the advantage of being faster than DRAM, although the disadvantage is that it is more expensive. SRAM is static in the sense that it doesn't require constant electrical refreshes; however, it still requires constant current to maintainthe voltage differentials. SRAM generally requires less power than DRAM.

Each bit in a SRAM chip requires a cell of six transistors, although DRAM needs only one transistor and one capacitor. This means that SRAM cannot achieve the storage densities of the DRAM family. As with DRAM, SRAM chips are mostly large arrays of these cells of transistors. The two primary applications of SRAM are embedded use and in computers.

## 1.4 READ ONLY MEMORY (ROM)

Memories in the ROM family are distinguished by the methods used to write new data tothem and the number of times they can be rewritten. Thisclassification reflects the evolution of ROM devices from hardwired to one-timeprogrammable to erasable-and-programmable. A common feature across all these devices istheir ability to retain data and programs forever, even during a power failure.

There are several types of read only memory (ROM), although most are obsolete. These ROMs are called read onlybecause they cannot be modified by the casual user (and some types cannot be modified at all). ROMs have traditionally been used

in computer systems to store configurationdata, such as bootstrap or BIOS code, which requires fast access.

#### 1.4.1 Masked ROMs

The very first ROMs were hardwired devices that contained a preprogrammed set of data orinstructions. The contents of the ROM had to be specified before chip production, so theactual data could be used to arrange the transistors inside the chip. Hardwired memories arestill used, though they are now called "masked ROMs" to distinguish them from other typesof ROM. The main advantage of a masked ROM is a low production cost. Unfortunately, thecost is low only when hundreds of thousands of copies of the same ROM are required.it was often usedto contain the startup code (bootstrap) for early microcomputers.

#### 1.4.2 Programmable Read Only Memory (PROM)

One step up from the masked ROM is the PROM (programmable ROM), which is purchasedin an unprogrammed state. The process of writing your data to the PROM involves a special piece of equipment called a device programmer. The deviceprogrammer writes data to the device one word at a time, by applying an electrical charge to the input pins of the chip. Once a PROM has been programmed in this way, its contents cannever be changed. If the code or data stored in the PROM must be changed, the current devicemust be discarded. As a result, PROMs are also known as *one-time programmable* (OTP)devices.

ThePROM is a cheaper and more flexible approach than mask ROM, although each PROMcan still be programmed only once. PROMs are reliable, permanent, and relatively fast. They are still in limited use.

#### 1.4.3 Erasable Programmable Read Only Memory (EPROM)

An EPROM (erasable-and-programmable ROM) is programmed in exactly the same manneras a PROM. However, EPROMs can be erased and reprogrammed repeatedly. To erase anEPROM, you simply expose the device to a strong source of ultraviolet light. (There is a"window" in the top of the device to let the ultraviolet light reach the silicon.) By doing this, you essentially reset the entire chip to its initial-unprogrammed-state. EPROM chips preserve their data for roughly10 to 20 years and allow for an unlimitednumber of reads. The erasing window is kept covered by a foil label to prevent erasure by exposure to sunlight.

The most popular use of EPROMs in computer systems was to store the BIOS in older PC systems. Though more expensive than

PROMs, their ability to be reprogrammed makes EPROMs an essential part of thesoftware development and testing process.

# 1.4.4 Electronically Erasable Programmable Read Only Memory (EEPROM)

The electronically erasable programmable read only memory (EEPROM) has largelysupplanted all other types of ROM in the current generation of computing devices. Thecapacity of EEPROMs ranges up to hundreds of kilobits. This is now the preferredtechnology for storing the BIOS in personal computers.

As the term electronically erasable implies, EEPROMs can be erased and rewritten, usually by creating a high-voltage pulse on the chip. This rewriting eventually damagesthe layer of insulating material on the chip, so the number of writes is limited. Althoughearly models would fail after 100 write-erase cycles, current EEPROMs can sustain onemillion write-erases or more. Any byte within an EEPROM can be erased and rewritten. Once written, thenew data will remain in the device forever-or at least until it is electrically erased. Thetradeoff for this improved functionality is mainly higher cost.

#### 1.4.5 Flash Memory

Flash memory is the most recent advancement in memory technology. It combines all the bestfeatures of the memory devices described thus far. Flash memory devices are high density,low cost, nonvolatile, fast (to read, but not to write), and electrically reprogrammable.Although flash memory is erased only one blockor page at a time, it is much less expensive than EEPROM.

Theseadvantages are overwhelming and the use of Flash memory has increased dramatically inembedded systems as a direct result. From а software viewpoint, Flash and EEPROMtechnologies are very similar. The major difference is that Flash devices can be erased onlyone sector at a time, not byte by byte. Typical sector sizes are in the range of 256 bytes to 16kilobytes. Despite this disadvantage, Flash is much more popular than EEPROM and israpidly displacing many of the ROM devices as well.

## 1.5 NONVOLATILE RAM (NVRAM)

An NVRAM is usually just anSRAM with a battery backup. When the power is turned on, the NVRAM operates just likeany other SRAM. But when the power is turned off, the NVRAM draws just enough electricalpower from the battery to retain its current contents. NVRAM is fairly common in embeddedsystems. However, it is very expensive-even more expensive than SRAM-so its applications are typically limited to the storage of only a few hundred bytes of system-critical information that cannot be stored in any better way.

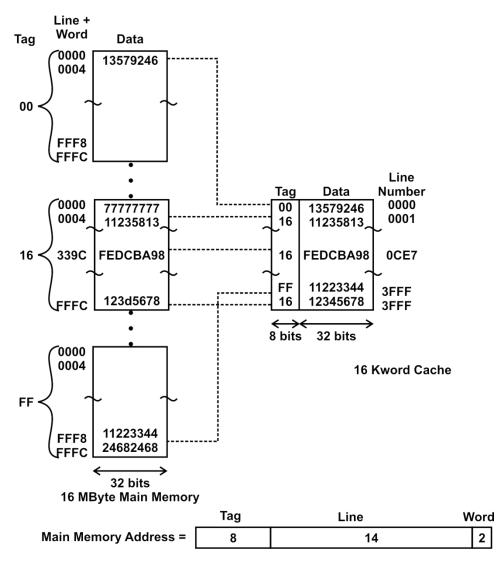

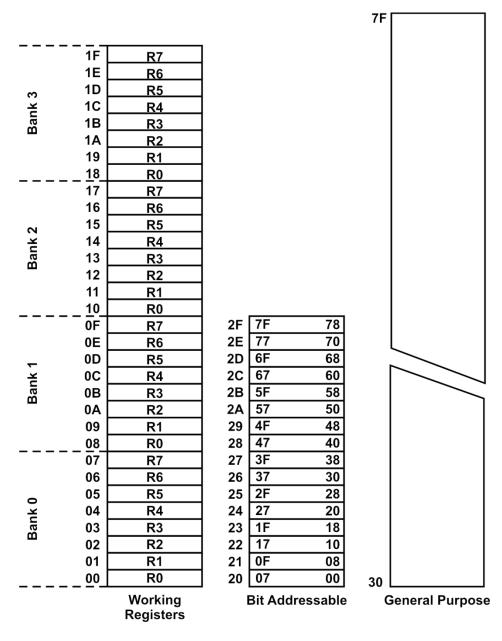

### 1.6 MEMORY INTERFACING

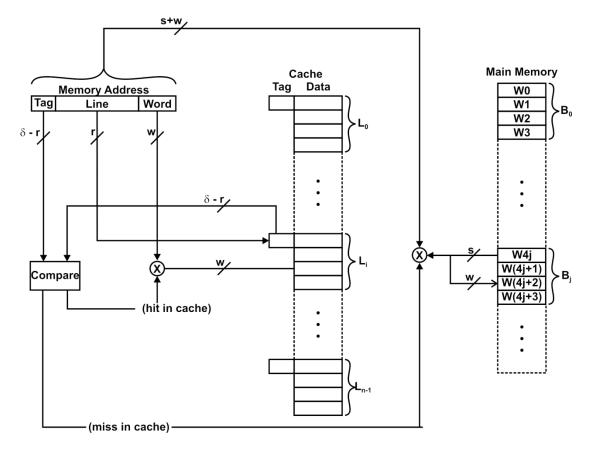

In computer systems, 1K=1024; therefore 1Kbyte memory chip has 1024 registers with 8 bits each. Similarly, a group of 256 registers is defined as one page and each register is viewed as a line to write on. This is analogous to a notebooks containing various pages, with each page having a certain numbers of lines. With this analogy, 1Kbyte memory as a chip of four pages (1024/256=4) with each page having 256 registers. With two hex digits, 256 registers can be numbered from 00H to FFH; 1024 registers can be numbered from four digits from 0000H to 03FFH. The high order two digits of 1 K memory are representing 4 pages (00, 01, 02 & 03)

#### **1.6.1 Memory Address**

In computer science, a memory address is a unique identifier for a memory location at which a CPU or other device can store a piece of data for later retrieval.In modern byte- addressable computers, each address identifies a single byte of storage.Some microprocessors were designed to be word-addressable, so that the typical storage unit was actually larger than a byte.

Each memory chip like RAM, ROM, EPROM, E<sup>2</sup>PROM and DRAM have numbers of pins and these pins are used to accept different kinds of signals.Normally every memory chip has pins for address, data, control signals and chip select signals.

#### 1.6.2 Address Pins

Address pins are used to accept address from the system address bus transmitted by the microprocessor. The numbers of address pins are depending upon size of the memory as shown in Table below

| Number of<br>Address ines used | Size of memory<br>in bytes |

|--------------------------------|----------------------------|

| 1                              | 2                          |

| 2                              | 4                          |

| 3                              | 8                          |

| 4                              | 16                         |

| 5                              | 32                         |

| 6                              | 64                         |

| 128         |

|-------------|

| 256         |

| 512         |

| 1024 ≈ 1k   |

| 2048 ≈ 2k   |

| 4096 ≈ 4k   |

| 8192 ≈ 8k   |

| 16384 ≈ 16k |

| 32768 ≈ 32k |

| 65536 ≈ 64k |

|             |

In case of 8085 microprocessor the address bus is 16 bit wide; it can address 65,536 locations i.e. 64 Kbytes of memory.

#### 1.6.3 <del>CS</del> (Chip Select) or <del>CE</del> (Chip Enable) Pin

This signal of the memory chip is ACTIVE LOW and acts as master enable pin for read or write operation.Hence, for every read or write operation, this signal must be low otherwise no operation will be performed.

#### 1.6.4 WR (Write Control Signal) Pin

This is an active low input control signal used to write data to the memory location whose address is available on address lines if chip select signal is enable.

This signal is available on system control bus and generated by the microprocessor or other master in the system such as DMA controller or co-processor.

#### 1.6.5 RD (Read Control Signal) Pin

This is an active low input control signal used to read data from the memory location whose address is available on address lines if chip select signal is enable.

This signal is available on system control bus and generated by the microprocessor or other master in the system such as DMA controller or co-processor.

#### 1.6.6 Chip Select Logic

Chip select logic can be developed using either combination of different gates such as AND, NAND, NOT etc. or decoders.

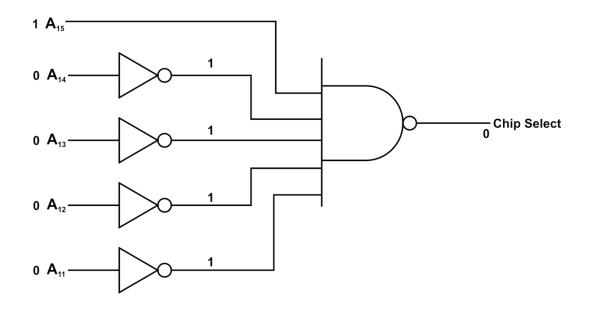

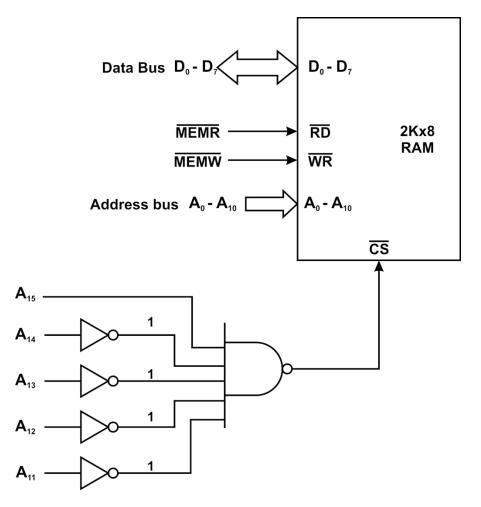

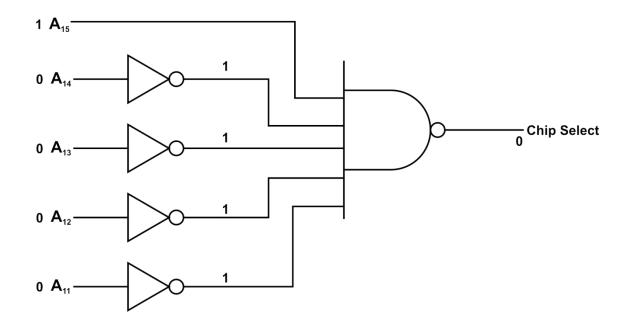

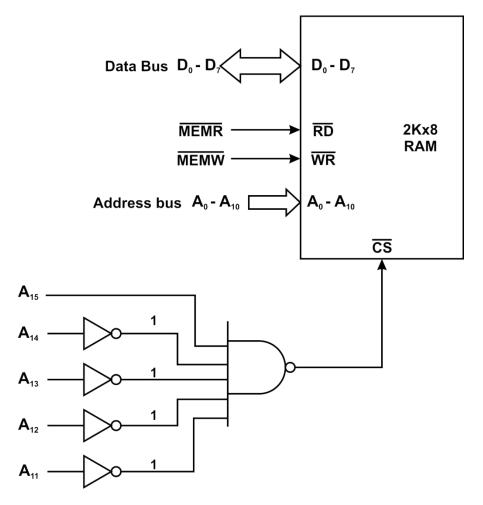

#### 1.6.6.1 Using Logic Gates

Now take an example of interfacing of 2K of RAM with the microprocessor 8085, the 8085 is an 8 bit microprocessor. Hence all 8 lines of data bus can be directly connected after de-

multiplexing to  $D_0$ - $D_7$  of the RAM memory. The eleven (11) address lines required to access any memory location within 2K memory, so out of 16 address lines (A<sub>0</sub>-A<sub>15</sub>) of 8085 microprocessor, the A<sub>0</sub>-A<sub>10</sub> address lines can be connected directly memory chip. Remaining address lines A<sub>11</sub>-A<sub>15</sub>to generate chip select signal using NAND and NOT gates depending on the addresses required as shown in following figure.

#### Fig 2.1 Chip select using NAND gates

For generation of chip select we are using NAND gate, when input to NAND gate are all logic 1, then output of NAND gate will be logic 0 and for all other combination the output will be logic 1.

The chip select is active low signal, hence all inputs of the NAND gates must be logic 1 to generate chip select signal as given below.

| A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|

| 1               | 0               | 0               | 0               | 0               |

А А А А А А А А А А А ADDR А А А А А ESS 0 10 6 5 15 14 13 12 11 9 8 1 0 0 0 0 0 0 0 0 0 0 8000H 1 0 0 0 0 0 0 1 1 87FFH 1 0 0 0 1 1 1 1 1 1 1 1 1 Used for Connected to A\_A<sub>10</sub> 2 K RAM chip select Decoder logic

Hence addresses map of the 2K of RAM is given below.

The interfacing diagram of 2K X 8 RAM is shown in following figure

Fig. 2.2 Interfacing of 2K X 8 RAM

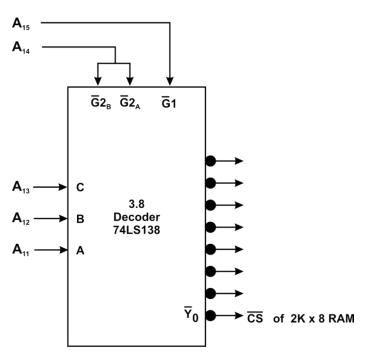

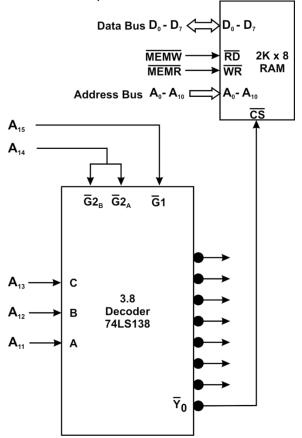

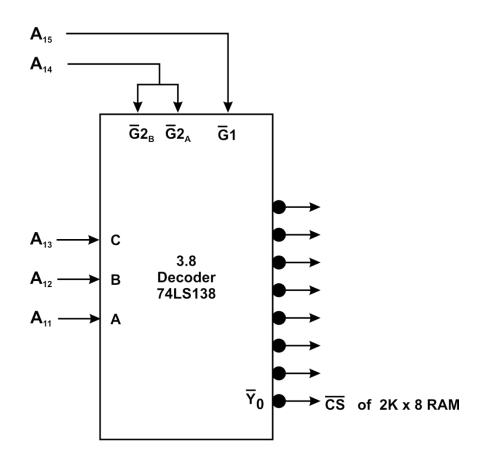

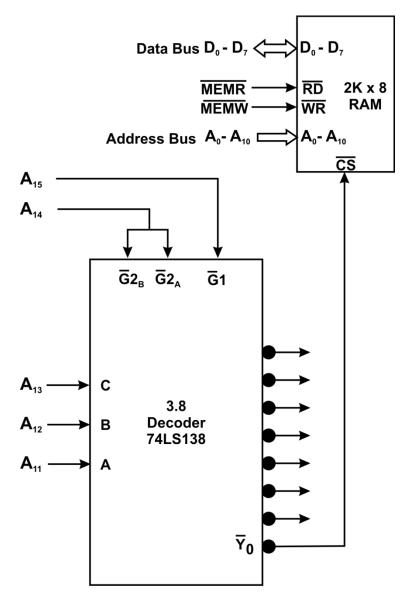

#### 1.6.6.2 Using Decoder

Consider above example of memory interfacing, where remaining address lines i.e.  $A_{11}$ - $A_{15}$  can be connected to the decoder. Now connect  $A_{11}$ ,  $A_{12}$ ,  $A_{13}$  to A, B,C inputs of 3:8 decoder 74LS138 respectively,  $A_{14}$  to  $G_{2A}$  and  $G_{2B}$  enable pins and at last  $A_{15}$  to  $G_1$  pin of 3:8 decoder as shown in following figure.

After making the connection as shown above, the address map of 2K RAM will be same as specified above.

Fig. 2.4Interfacing of 2K X 8 RAM using decoder chip select logic

Here, the advantage of using decoder is minimum hardware is required as compared using NAND gates. When we use NAND gates, other logical devices are also required as per requirement as in above examples, NOT gates are used. Hence for numbers of devices, numbers of NAND and other logical devices are required to generate chip select signals.

But when we use decoder like 3:8 (74LS138), we can generate eight chip select signals using one decoder IC, as it has eight active low output pins. The complete interfacing diagram using decoder to generate chip select signals for 2K of RAM is shown in Fig. 2.4

# 1.7 SUMMARY

- Most computers incorporate two types of volatile RAM: static and dynamic.

- DRAM stores each bit of information in a separate capacitor on the integrated circuit. With using capacitors for storage is that they gradually dissipate their charge, so the charge must be refreshed regularly.

- The DRAM controller is an extra piece of hardware placed between the processor and the memory chips. Its main purpose is to perform the refresh operations required to keep your data alive in the DRAM.

- Static RAM (SRAM) has the advantage of being faster than DRAM, although the disadvantage is that it is more expensive.

- The process of writing your data to the PROM involves a special piece of equipment called a device programmer.

- EPROMs can be erased and reprogrammed repeatedly. To erase anEPROM, you simply expose the device to a strong source of ultraviolet light.

- EEPROMs can be erased and rewritten, usually by creating a high-voltage pulse on the chip.

- Flash memory devices are high density, low cost, nonvolatile, fast (to read, but not to write), and electrically reprogrammable.

- > An NVRAM is usually just anSRAM with a battery backup.

- In case of 8085 microprocessor the address bus is 16 bit wide; it can address 65,536 locations i.e. 64 Kbytes of memory.

- Chip select logic can be developed using either combination of different gates such as AND, NAND, NOT etc. or decoders.

# 1.8 **REVIEW QUESTIONS**

- Q.1 Distinguish between SRAM & DRAM.

- Q.2 Write a short note on RAM.

- Q.3 Explain different types of ROM.

- Q.4 Distinguish between EPROM & EEPROM.

- Q.5 Write a short note on Flash memory.

- Q.6 Explain memory interfacing in 8085.

- Q.7 Explain control signalsWR, RD and chip select logic.

# **1.9 REFERENCE**

- Microprocessor Architecture, Programming, and Applications With the 8085 by Ramesh Gaonkar, Publisher:Prentice Hall

- Programming Embedded Systems in C and C++ by Michael Barr, Publisher: O'Reilly

# INTRODUCTION TO 8085 MICROPROCESSOR

# **Topics Covered:**

3.1 Introduction

- 3.2 Organization of Microprocessor based System

- 3.3 Features of 8085 Microprocessor

# **3.1 INTRODUCTION**

- ⇒ The microprocessor [MPU] is a programmable digital device, designed with registers, flip-flops and timing elements.

- ⇒ The microprocessor has a set of instructions, designed internally, to manipulate data and communicate with peripherals. This process of data manipulation and communication is determined by the logic design of the microprocessor, called architecture.

- ⇒ The microprocessor can be programmed to perform functions on given data by selecting necessary instructions from its set.

- ⇒ These instructions are given to the microprocessor by writing them into its memory.

- ➡ Writing instructions and data is done through input device such as keyboard.

- ⇒ The functions performed by microprocessor can be classified into following categories:

- Microprocessor initiated operations.

- Internal operations.

- Peripheral (or eternally initiated) operations.

# Microprocessor – Initiated operations and 8085 Bus organization:

- ⇒ The MPU performs primarily four operations:

- 1. Memory Read: Reads data (or instructions) from memory.

- 2. Memory Write: Writes data (or instructions) into memory.

- 3. I/O Read: Accepts data from input devices.

- 4. I/O Write: Sends data to output devices.

- All these operations are part of communication process between the MPU and peripheral devices.

- ➡ To communicate with peripheral (or memory location), the MPU needs to perform the following steps:

Step 1: Identify the peripheral or the memory location (with its address)

Step 2: Transfer binary information (data and instruction)

Step 3: Provide timing or synchronization signals.

- ⇒ The 8085 MPU performs these functions using three sets of communication lines called buses:

- Address bus

- Data bus

- Control bus

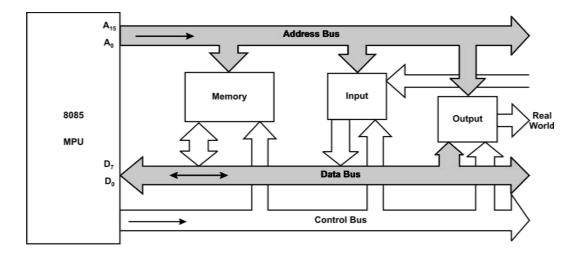

Fig. 3.1 The 8085 Bus Structure

#### Address Bus:

- ⇒ The address bus is a group of 16-lines generally identified as A<sub>0</sub> to A<sub>15</sub>.

- ⇒ The address bus is unidirectional: bits flow in one directionfrom the MPU to peripheral devices.

- ⇒ The MPU uses address bus to perform the first function: identifying a peripheral or a memory location.

- ⇒ In a computer system, a binary number called an address identifies each peripheral or memory location, and the address bus is used to carry a 16-bit address.

- ⇒ The number of address lines of the MPU determines its capacity to identify different memory locations (on peripherals).

- ⇒ The 8085 MPU with 16 address lines capable of addressing 65536 (generally known as 64K) memory locations.

- ➡ E.g. Intel 8088 processor has 20 address lines and Pentium processor has 32 address lines.

#### Data Bus:

- ⇒ The data bus is a group of 8 lines used for data flow (the term data refers to any binary information that may include an instruction, an address or a number).

- ⇒ These lines are bi-directional- data flow in both directions between MPU and memory and peripheral devices.

- ⇒ The MPU uses data bus to perform second function: transferring binary information.

- ➡ To eight data lines enable the MPU to manipulate 8-bit data ranging from 00 to FF.

- ⇒ The largest number that can appear on the data bus is 1111 1111. The 8085 is known as an 8-bit microprocessor.

- ➡ Microprocessors such as Intel 8086, Zilog Z8000 and Motorola 68000 have 16 data lines; thus they are known as 16-bit microprocessor.

- ⇒ Intel 80386/486/586 are 32-bit microprocessor.

#### Control Bus:

- ⇒ The control bus is the various signal lines that carry synchronization signals.

- ⇒ The MPU generates specific control signals for every operation (such as Memory Read or I/O Write) it performs.

- ⇒ The MPU places the 16-bit address on the address bus.

- ⇒ The address on the bus is decoded by an external logic circuit.

- ⇒ The MPU sends a pulse called Memory Read as the control signal.

⇒ The pulse activates the memory chip, and the contents of the memory location are placed on the data bus and brought inside the microprocessor.

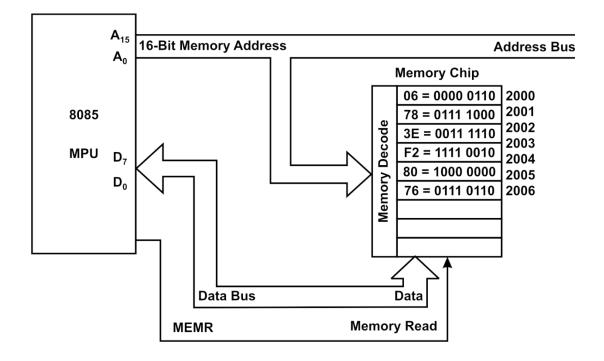

Fig. 3.2 Memory Read Operation

#### Internal Data Operations and the 8085 Registers:

- ⇒ The 8085 performs operations on data such as arithmetic, logical operations, stores data, test for conditions etc.

- ➡ To perform these operations MPU requires registers, ALU and control logic and internal buses.

- ➡ Consider the following hex codes of the instructions stored in memory locations from 2000H to 2005H as follows:

| 2000 | 06 | MVI B, 78H |

|------|----|------------|

| 2001 | 78 |            |

| 2002 | 3E | MVI A, F2H |

| 2003 | F2 |            |

| 2004 | 80 | ADD B      |

| 2005 | 76 | HLT        |

Fig. 3.3 8085 Programmable Registers

- ⇒ When user enters the memory address 2000H. The processor places the address 2000H in the Program Counter (PC).

- 1. When processor begins execution it places the address 2000H on the address bus and increment the address in the PC to 2001 for the next operation. It brings the code 06, interprets the code, and places the address 2001 H on the address bus, and then gets byte 78 H and increment the address in PC to 2002H. The processor repeats the same process for the next instruction MVI A, F2H.

- 2. When processor executes the first two instructions, it uses register B to store 78H and register A to store F2H.

- When processor executes the instruction ADD B in the ALU it adds 78H and F2H and result is placed in Accumulator (78H + F2H = 16AH). It replaces F2H by 6AH in A and sets Carry flag.

- 4. In the above addition operation generates the Carry. Therefore the Carry flag (CY) = 1 is set.

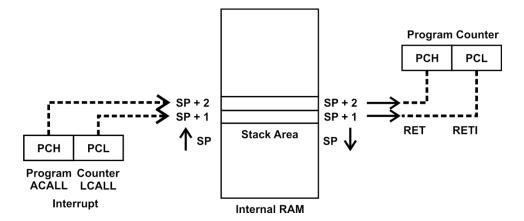

- 5. The fifth operation deals with concept of stack. The stack pointer is a 16-bit register used as a memory pointer to identify the stack, part of R/W memory defined and used by the processor for temporary storage of data during the execution.

#### Peripheral or Externally Initiated Operations:

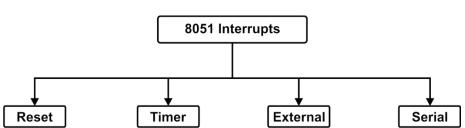

External devices (or signals) can initiate the following operations, for which individual pins on the microprocessor chip are assigned: Reset, Interrupt, Ready, Hold.

**Reset:** When an external key activates RESET key, all internal operations are suspended and the program counter is cleared (it holds 0000H). Now program execution begins at the zero memory address.

**Interrupt:** The microprocessor can be interrupted from the normal execution of instructions and asked to execute some other instructions called a service routine. The microprocessor resumes its operation after completing the service routine.

**Ready:** The 8085 has a pin called READY. If the signal at this READY pin is low, the microprocessor enters into a Wait state. This signal is used primarily to synchronize slower peripherals with the microprocessor.

**Hold:** When the HOLD pin is activated by an external signal, the microprocessor relinquishes control of buses and allows the external peripherals to use them. HOLD signal is used in Direct Memory Access (DMA) data transfer.

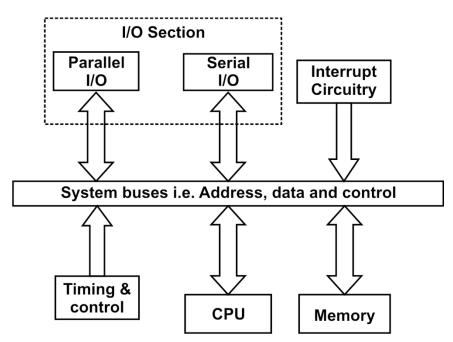

# 3.2 ORGANIZATION OF MICROPROCESSOR BASED SYSTEM

- A microprocessor based system has standard components like memory, timing and input/output.

- ⇒ Depending on the application, other components are added such as digital to analog converter, interval timer, math coprocessors, interrupt controller etc.

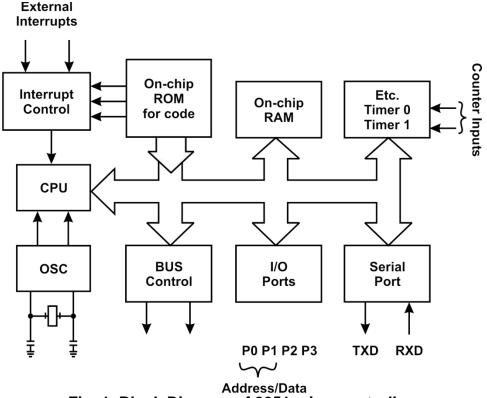

- Figure below shows the basic block diagram of microprocessor based system containing some standard components.

#### Fig. 3.4 Basic block diagram of Microprocessor Based System

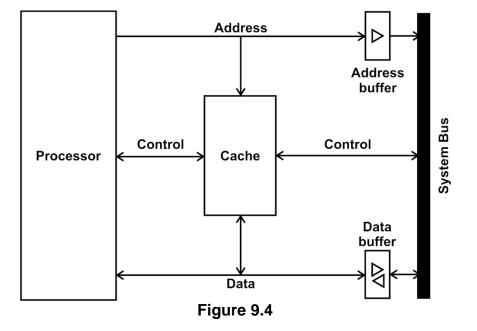

⇒ All components of the system communicate via system buses i.e address, data and control buses.

#### Central Processing Unit [CPU]

- ⇒ The CPU is the heart of the system, the master controller of all operations that can be performed.

- ⇒ It reads instruction from the memory then decodes and finally executes that instruction to perform desired operation.

- ⇒ The CPU is also responsible to generate all necessary control signals and control other components in the system.

- ⇒ The CPU section consists of a microprocessor and the associated logic circuitry required enabling the CPU to communicate with the other components in the system via system buses.

- ⇒ This logic may consist of data and address driver for communication.

- ⇒ The actual microprocessor used depends on the complexity of the task that will be controlled or performed by the system.

#### Memory

- ➡ It has two components i.e read only memory [ROM] and random access memory [RAM].

- Sometimes other semiconductor memories such as EPROM, PROM, E<sup>2</sup>PROM can be used and usually contains monitor programs or BIOS program.

- ⇒ The ROM included provides the system with its intelligence, which is needed at the start up (power on) to configure or initialize peripheral.

- $\Rightarrow$  The RAM is of again two types i.e static and dynamic RAM.

- ⇒ The static RAM is fast and easy to interface, but comes in small sizes and costly.

- ⇒ The dynamic RAM is slow and requires numerous refreshing cycles to retain the stored data, even so dynamic RAM is the choice for large memory where large amount of data can be stored as these RAM's are cheaper in cost.

- ⇒ Both static and dynamic RAM lose their information, when power is turned off, which may cause a problem in certain situations.

- ⇒ In the latest systems, non-volatile memory (NVM) is used which retains its information even when power is turned off.

- ⇒ NVM comes in a small size; hence it is used to store only the most important information during power failure.

#### Timing and Control

- ⇒ This section of the system governs all system timing and thus is responsible for the proper operation of the entire system hardware.

- ⇒ The timing section usually consists of a crystal oscillator and timing circuitry set to operate the microprocessor at its specified clock rate.

#### I/O Section

Some system may require the I/O peripherals for the some specific purpose such as keyboard for entering data and program, monitor to display results, printers to get hard copy etc.

- So, microprocessor can communicate with these peripheral either using parallel or serial communication port.

- Serial communication is slow but it has advantage of simplicity i.e requires only two wires for receive, transmit and ground.

- ⇒ Serial communication is easily adapted for use in fibre optics cables.

- On other hand, parallel I/O is faster but requires more lines depending on size of data bus hence it is costly for implementation.

- A parallel I/O operation can be used to transfer data to/from a hard disk, reading switch information, controlling indicator lights, transferring data to A/D or D/A converter and other types of parallel devices.

#### Interrupt Circuitry

- ⇒ When a microprocessor used in control applications, there will be times when the system must respond to special external circumstances.

- Such circumstances interrupt the microprocessor from its normal execution to service the unexpected event.

- ⇒ The system software is designed to handle such unexpected event.

- ⇒ Interrupts are used to perform a special task such as real time clocks, multitasking capability and fast I/O operations.

- ⇒ The interrupt circuitry needed from system to system will vary depending on the applications.

# 3.3 FEATURES OF 8085 MICROPROCESSOR

- ⇒ 8085 microprocessor is an 8-bit microprocessor.

- ⇒ It can accept process or provide 8-bit data simultaneously.

- ➡ It operates on a single +5v power supply connected at Vcc and power supply ground is connected to Vss.

- $\Rightarrow$  It can operate on clock cycle with 50% duty cycle.

- $\Rightarrow$  It has on chip clock generator.

- ⇒ This internal clock generator requires tuned circuit like LC, RC or crystal.

- $\Rightarrow$  It can operate with a 3 MHz clock frequency.

- ➡ It has 16 address lines; hence it can access 64 kbytes of memory.

- ⇒ It provides 8 bit I/O addresses to access 256 I/O ports.

# 3.4 EXERCISE

- 1. What is a Microprocessor?

- 2. Explain the classification of the functions performed by the Microprocessor.

- 3. List the four operations commonly performed by the Microprocessor.

- 4. Explain the three set of communication lines used to perform the functions of 8085 microprocessors.

- 5. What is a bus?

- 6. Specify the function of the address bus and the direction of the information flow on the address bus.

- 7. Why is the data bus bidirectional?

- 8. Explain Control Bus.

- 9. What are the various operations performed by the 8085 Microprocessor on the data?

- 10. Specify the four control signals commonly used by the 8085 microprocessor.

- 11. Explain with diagram Microprocessor Based System.

- 12. What are the features of 8085 Microprocessor?

## 3.5 **REFERENCES**

Computer System Architecture – M. Morris Meno, PHI, 1998

Computer Architecture and Organization - John P Hayes, McGraw Hill, 1998

Digital Computer Fundamentals – Malvino

Digital Computer Fundamentals – Thomas C Bartee, TMG

Computer Organization and Architecture – William Stallings

Microprocessor Architecture and Programming and Applications with the 8085 – R.S. Gaonkar, PRI

# PIN DIAGRAM AND ARCHITECTURE OF 8085 MICROPROCESSOR

#### **Topics Covered:**

- 4.1 Pin Diagram of 8085 Microprocessor with description

- 4.2Architecture of 8085 Microprocessor

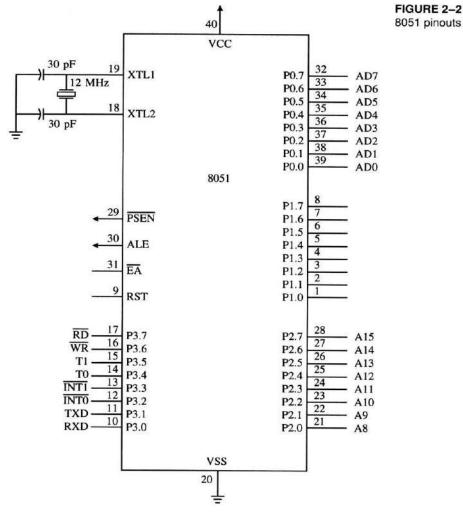

# 4.1 PIN DIAGRAM OF 8085 MICROPROCESSOR WITH DESCRIPTION

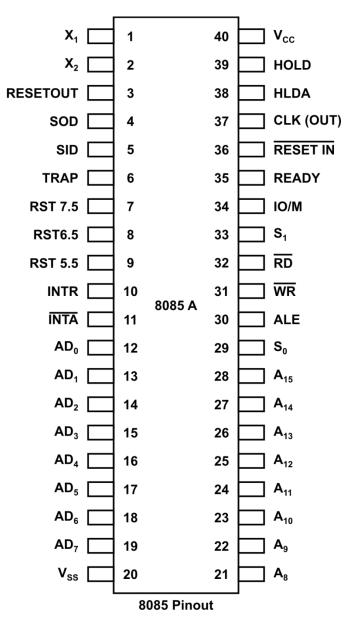

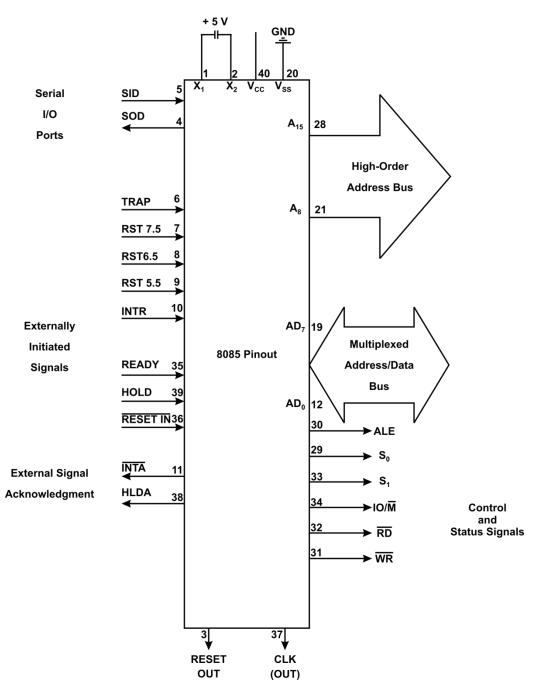

#### The 8085 microprocessor

- ⇒ 8085 is a 8-bit general purpose microprocessor capable of addressing 64K memory. The device has 40 pins and requires +5V single power supply. It can operate with 3MHz single-phase clock.

- ⇒ The logic pin out of the 8085-microprocessor signals can be classified into six groups:

- 1. Address bus

- 2. Multiplexed Address/Data bus

- 3. Control and status signals

- 4. Power supply and clock frequency

- 5. Externally initiated signals, including interrupts

- 6. Serial I/O ports

Fig. 4.1 Pin Diagram of 8085 Microprocessor

Fig. 4.2 The Signals of 8085 Microprocessor

#### Address Bus:

⇒ The 16 address lines are split into two parts A<sub>15</sub>-A<sub>8</sub> and AD<sub>7</sub>-AD<sub>0</sub>. Higher order bus is unidirectional and the signal lines AD<sub>7</sub>-AD<sub>0</sub> are used for a dual purpose.

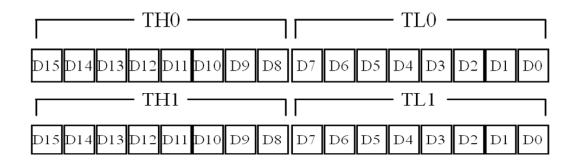

#### Multiplexed Address/Data Bus:

⇒ The signal lines AD<sub>7</sub>-AD<sub>0</sub> are bi-directional. They are used as lower order address bus as well as data bus. In executing an instruction, during the earlier part of the cycle, these lines are used as low order address bus. During later part of cycle these lines are used are data bus.

34

#### **Control and Status Signals:**

- This group of signals includes two control signals RD and WR, three status signals (IO/M, S1 and S0) to identify nature of operation.

- ALE (Address Latch Enable) : This is a +ve pulse generated every time when 8085 begins an operation(machine cycle); it indicates that the bits on AD<sub>7</sub>-AD<sub>0</sub> are address bits. This signal is primarily used to latch the low-order address bus.

- **RD-(Read) :** This is a Read control signal(Active low). This signal indicates that the selected I/O or memory device is to be read and data are available on data bus.

- **WR-(Write)** : This is a Write control signal(Active low). This signal indicates that the data on the data bus are to be written into a selected memory or I/O location.

- **IO/M** : This is a status signal used to differentiate between I/O and memory operations. When it is high, it indicates an I/O operation; when it is low, it indicates a memory operation. This signal is combined with RD and WR to generate I/O and memory control signals.

- **S1 and S0 :** These status signals are similar to IO/M and used to identify various operation as follows

| Machine Cycle            | Status    |        |            | Control       |

|--------------------------|-----------|--------|------------|---------------|

|                          | IO/M      | S1     | <b>S</b> 0 | signals       |

| Opcode Fetch             | 0         | 1      | 1          | RD=0          |

| Memory Read              | 0         | 1      | 0          | RD=0          |

| Memory Write             | 0         | 0      | 1          | WR=0          |

| I/O Read                 | 1         | 1      | 0          | RD=0          |

| I/O Write                | 1         | 0      | 1          | WR=0          |

| Interrupt<br>Acknowledge | 1         | 1      | 1          | INTA=0        |

| Halt                     | Z         | 0      | 0          |               |

| Hold                     | Z         | Х      | Х          | RD,WR=Z       |

| Reset                    | Z         | Х      | Х          | and<br>INTA=1 |

| 7                        | -liah imr | adanaa | V Llna     | pacified      |

Table 4.1 8085 Machine Cycle Status and Control Signals

Z= High impedance X=Unspecified

#### • Power Supply and Clock Frequency:

The power supply and frequency signals are as follows  $V_{cc}$ : +5V power supply  $V_{cc}$ : Ground Reference

V<sub>ss</sub> : Ground Reference

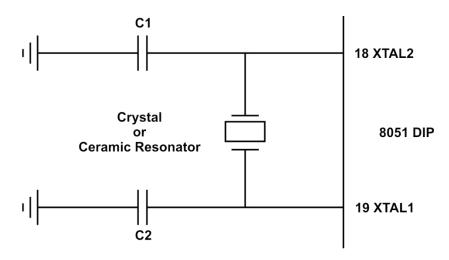

$X_1$ ,  $X_2$ : A crystal is connected at these two pins. The frequency is internally divided by two; therefore to operate a system at 3MHz the crystal should have frequency of 6MHz. CLK(OUT) : Clock output. This signal can be used as the system clock for other devices.

#### Externally initiated signals, including interrupts:

- ⇒ The 8085 has five interrupt signals that can be used to interrupt program execution. The microprocessor acknowledges the interrupt request by INTA signal.

- ⇒ In addition to interrupts, three pins- RESET, HOLD and READY – accept the externally initiated signals as inputs. To respond to the HOLD request, the 8085 has one signal HLDA (Hold Acknowledge).

#### **RESET IN:**

⇒ When the signal on this pin goes low, the program counter is set to zero the buses are tri-stated and the MPU is Reset.

#### **RESET OUT**

⇒ This signal indicates that the MPU is being Reset. The signal can be used to Reset other devices.

| Interrupt                              | Description                                                                                                                                                                                                                         |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR (Input)                           | Interrupt Request: This is used as a general purpose interrupt; it is similar to INT of 8080A                                                                                                                                       |

| INTA (Output)                          | Interrupt Acknowledge: This is used to Acknowledge the interrupt.                                                                                                                                                                   |

| RST 7.5 (Inputs)<br>RST 6.5<br>RST 5.5 | Restart Interrupts: These are vectored interrupts<br>that transfer the program control to specific<br>memory locations. They have higher priorities<br>than INTR interrupt. Among these three priority<br>order is 7.5, 6.5 and 5.5 |

| TRAP (Input)                           | This is non mask able interrupt and has highest priority.                                                                                                                                                                           |

| HOLD (Input)                           | This signal indicates the peripherals such as DMA (Direct Memory Access) controller are requesting the use of the address and data buses.                                                                                           |

| HLDA (Output) | Hold Acknowledge: This signal acknowledges the HOLD request.                                                                                                                                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READY (Input) | This signal is used to delay the microprocessor<br>Read or Write cycles until a slow-responding<br>peripheral is ready to send or accept data. When<br>this signal goes low, the microprocessor waits<br>for an integral number of clock cycles until it<br>goes high. |

Table 4.2 8085 Interrupts and Externally Initiated Signals

#### Serial I/O Ports:

- ⇒ The 8085 has two signals to implement the serial transmission: SID (Serial Input Data) and SOD (Serial Output Data).

- ⇒ In serial transmission, data bits are sent over a single line, one bit at a time, such as a transmission over telephone lines.

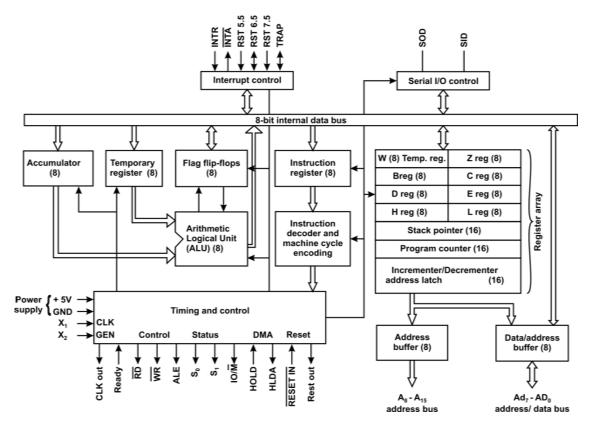

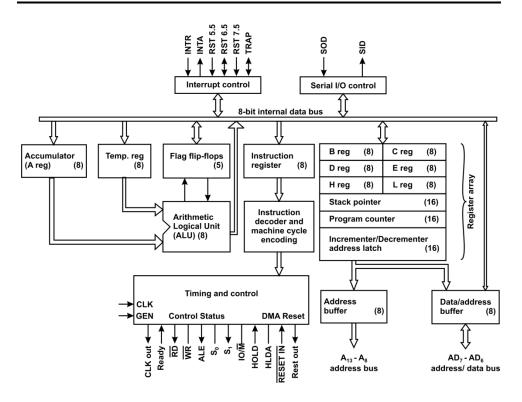

# 4.2 ARCHITECTURE OF 8085 MICROPROCESSOR

The architecture of the 8085 Microprocessor is shown below:

Fig. 4.3 Block diagram of 8085 microprocessor

#### Control Unit

- ⇒ Generates signals within microprocessor to carry out the instruction, which has been decoded.

- ⇒ In reality causes certain connections between blocks of the microprocessor to be opened or closed, so that data goes where it is required, and so that ALU operations occur.

#### **Arithmetic Logic Unit**

- ⇒ The ALU performs the actual numerical and logic operation such as 'add', 'subtract', 'AND', 'OR', etc.

- ⇒ Uses data from memory and from Accumulator to perform arithmetic.

- ⇒ Always stores result of operation in Accumulator.

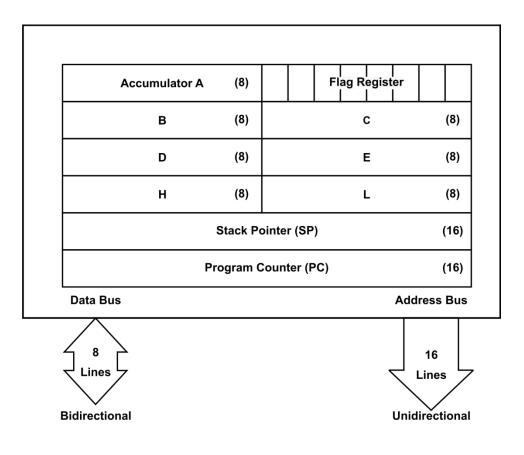

#### Registers

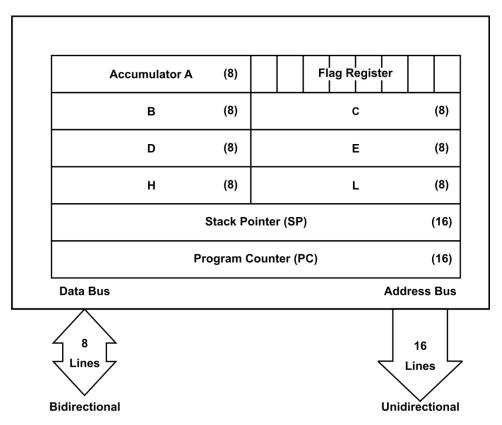

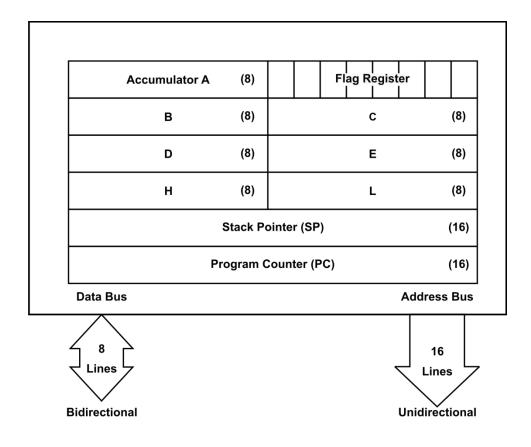

⇒ The 8085programming model includes six registers, one accumulator, and one flag register, as shown in Figure.

#### Fig. 4.4 The 8085 Programmable Registers

⇒ In addition, it has two 16-bit registers: the stack pointer and the program counter.

- ⇒ They are described briefly as follows.

- ⇒ The 8085/8080A has six general-purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L as shown in the figure.

- ⇒ They can be combined as register pairs BC, DE, and HL to perform some 16-bit operations.

- ⇒ The programmer can use these registers to store or copy data into the registers by using data copy instructions.

#### Accumulator

- ⇒ The accumulator is an 8-bit register that is a part of arithmetic/logic unit (ALU).

- ⇒ This register is used to store 8-bit data and to perform arithmetic and logical operations.

- $\Rightarrow$  The result of an operation is stored in the accumulator.

- $\Rightarrow$  The accumulator is also identified as register A.

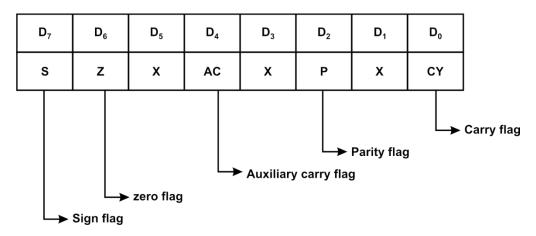

#### Flags

- ⇒ The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of the result in the accumulator and other registers.

- ⇒ They are called Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags.

- ⇒ The most commonly used flags are Zero, Carry, and Sign.

- ⇒ The microprocessor uses these flags to test data conditions.

- ⇒ For example, after an addition of two numbers, if the sum in the accumulator id larger than eight bits, the flip-flop uses to indicate a carry -- called the Carry flag (CY) -- is set to one.

- ⇒ When an arithmetic operation results in zero, the flip-flop called the Zero (Z) flag is set to one.

- ⇒ The figure shows an 8-bit register, called the flag register, adjacent to the accumulator.

#### Fig. 4.5 Format of flag registers of 8085 register

- ➡ However, it is not used as a register; five bit positions out of eight are used to store the outputs of the five flip-flops.

- ⇒ The flags are stored in the 8-bit register so that the programmer can examine these flags (data conditions) by accessing the register through an instruction.

- ⇒ These flags have critical importance in the decision-making process of the microprocessor.

- The conditions (set or reset) of the flags are tested through the software instructions. For example, the instruction JC (Jump on Carry) is implemented to change the sequence of a program when CY flag is set.

- ⇒ The thorough understanding of flag is essential in writing assembly language programs.

#### Program Counter (PC)

- ⇒ This 16-bit register deals with sequencing the execution of instructions.

- ⇒ This register is a memory pointer.

- ➡ Memory locations have 16-bit addresses, and that is why this is a 16-bit register.

- ⇒ The microprocessor uses this register to sequence the execution of the instructions.

- ⇒ The function of the program counter is to point to the memory address from which the next byte is to be fetched.

40

⇒ When a byte (machine code) is being fetched, the program counter is incremented by one to point to the next memory location.

#### Stack Pointer (SP)

- ⇒ The stack pointer is also a 16-bit register used as a memory pointer.

- ➡ It points to a memory location in R/W memory, called the stack.

- ⇒ The beginning of the stack is defined by loading 16-bit address in the stack pointer.

- ⇒ The stack concept is explained in the chapter "Stack and Subroutines."

#### Instruction Register/Decoder

- $\Rightarrow$  Temporary store for the current instruction of a program.

- ⇒ Latest instruction sent here from memory prior to execution.

- ⇒ Decoder then takes instruction and 'decodes' or interprets the instruction.

- $\Rightarrow$  Decoded instruction then passed to next stage.

#### Memory Address Register

- ➡ Holds address, received from PC, of next program instruction.

- ⇒ Feeds the address bus with addresses of location of the program under execution.

#### **Control Generator**

- ➡ Generates signals within microprocessor to carry out the instruction which has been decoded.

- ➡ In reality causes certain connections between blocks of the uP to be opened or closed, so that data goes where it is required, and so that ALU operations occur.

#### **Register Selector**

- ⇒ This block controls the use of the register stack in the example.

- ⇒ Just a logic circuit which switches between different registers in the set will receive instructions from Control Unit.

#### General Purpose Registers

- ⇒ Microprocessor requires extra registers for versatility.

- ⇒ Can be used to store additional data during a program.

- ➡ More complex processors may have a variety of differently named registers.

#### 8085 System Bus

- ➡ Typical system uses a number of buses i.e collections of wires, which transmit binary numbers, one bit per wire in term of voltage levels 0 volt or 5 volt for 0 and 1 respectively.

- A typical microprocessor communicates with memory and other devices input and output using three busses i.e Address bus, Data bus and Control bus.

#### Address Bus

- One wire is required for each bit, therefore 16 bits requires 16 wires. Binary number carried by these wires tells memory to open the designated memory location. Binary data can then be store in or taken out from the memory location depending on the control signal.

- ⇒ The Address bus consists of 16 wires, therefore its "width" is 16 bits.

- A 16 bit binary number allows 2<sup>16</sup> or 64K different numbers i.e 000000000000000 up to 111111111111111.

- ⇒ Because size of memory location is of 8 bit each, each with a unique address, the size of the address bus determines the size of memory which can be accessed.

- ➡ To communicate with memory the microprocessor sends an address on the address bus, e.g 00000000000011 (3 in decimal), to the memory.

- ⇒ The memory selects location number 3 for reading or writing data.

- Address bus is unidirectional, i.e numbers only sent from microprocessor to memory, not other way.

#### Data Bus

⇒ Data Bus carries 'data', in binary form, between microprocessor and other external devices such as memory or peripherals.

- Size of data bus is determined by the size of location in memory and data bus size helps determine performance of microprocessor.

- ⇒ The Data Bus is typically of 8 bit, 16 bit or 32 bit and it is bidirectional.

- ⇒ 8085 has 8 bit data bus, therefore 28 combinations of binary digits are possible.

- ⇒ Data bus used to transmit "data", i.e information, results of arithmetic, etc between memory and the microprocessor.

- ⇒ Therefore larger number has to be broken down into chunks of 255, this slows microprocessor.

- ⇒ Data Bus also carries instructions from memory to the microprocessor.

- ⇒ Size of the bus therefore limits the number of possible instructions to 256, each specified by a separate number.

#### **Control Bus**

- ⇒ Control bus is unidirectional.

- ➡ How can we tell the address is a memory address or an I/O port address and read/write data from/to memory or I/O port?

- ⇒ Normally control signal are of following types:

- o Memory Read

- Memory Write

- I/O Read

- I/O Write

- ⇒ When Memory Read or I/O Read is active, data is input to the processor.

- ⇒ When Memory Write or I/O Write is active, data is output from the processor.

- ⇒ The control bus signals are defined from the processor's point of view.

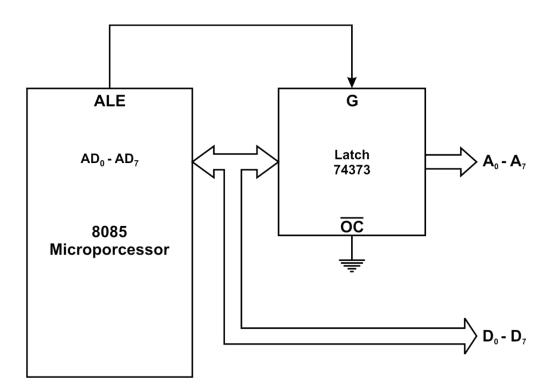

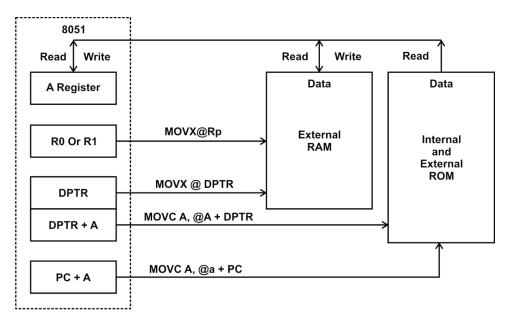

#### **De-Multiplexing of Address/Data Bus of 8085**

In the 8085 microprocessor, the higher order address lines i.e A<sub>8</sub>-A<sub>15</sub> are directly available, but the lower order address lines are multiplexed with data bus in time sharing.

- ➡ Hence the de multiplexing of address/data bus is required i.e separation of address and data bus.

- In T₁ state of every machine cycle, the contents on AD₀-AD₂ is the lower order address i.e A₀-A₂ and at the same time, the ALE also goes high for half of T₁ state.

- After T₁ state, the 8085 remove the contents of AD₀-AD₂ lines and use same lines as a data lines [data bus] for next clock cycle T₂ state onwards.

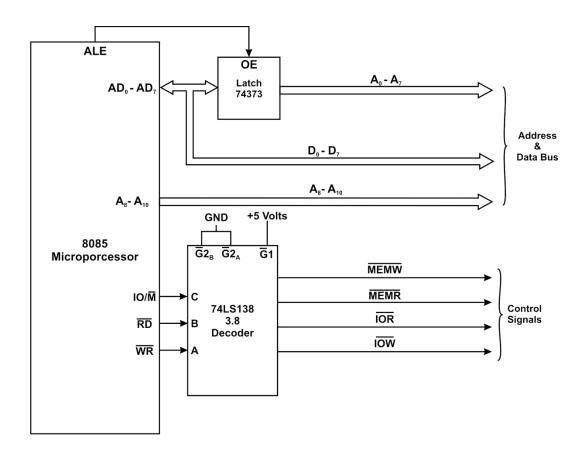

- ➡ Hence, the de-multiplexing of address/data bus can be implemented by using tri-state octal latch 74LS373 and this latch can be controlled by using ALE signal of 8085 as shown in the following figure:

#### Fig. 4.6 De-multiplexing of AD<sub>0</sub>-AD<sub>7</sub>

- ⇒ When ALE goes high, the address signals will be latched in the octal latch 74LS373 and output of the latch will be provided on A<sub>0</sub>-A<sub>7</sub>.

- ⇒ When ALE goes low, the latch will be disabled and the  $AD_0$ - $AD_7$  can be used as data bus  $D_0$ - $D_7$ .

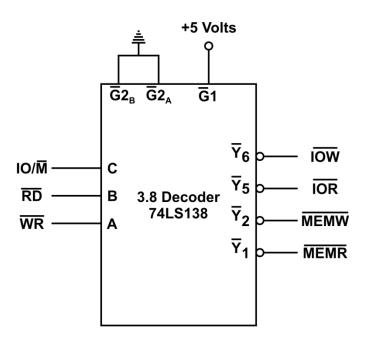

#### **Generation of Control Signal**

- ⇒ The Control signals required are RD and WR, but in any microprocessor based system, we will find memory devices as well as I/O devices.

- ➡ Hence, the control signals required are MEMR, MEMW, IOR and IOW and normally used to distinguish between memory and I/O devices. These signals can be generated by using 3:8 decoder 74LS138 as shown in figure below:

Fig. 4.7 Generation of Control Signal

#### Typical 8085 System Configuration

- The typical 8085 system can be designed using decoder (74LS138) to generate different control signals, latch 74LS373 to de-multiplexed address/data bus i.e separate address and data bus.

- ⇒ The device 72LS245 Octal Transceiver is optional but in buffered system is required.

- ⇒ The typical 8085 based system configuration is shown in figure below:

Fig. 4.8 Typical 8085 based system configuration

#### Address Decoding Techniques

- As we know, 8085 has 16 address lines using which allows addressing up to 64 KB of main memory.

- ⇒ Most of the time we do not need complete 64KB memory, so most of the address lines will remain free which can be used generate chip select and determine the range of the addresses the memory will occupy.

- ⇒ There are two types of decoding technique depending on the number of lines used for the decoder.

- Full or absolute decoding

- o Partial decoding

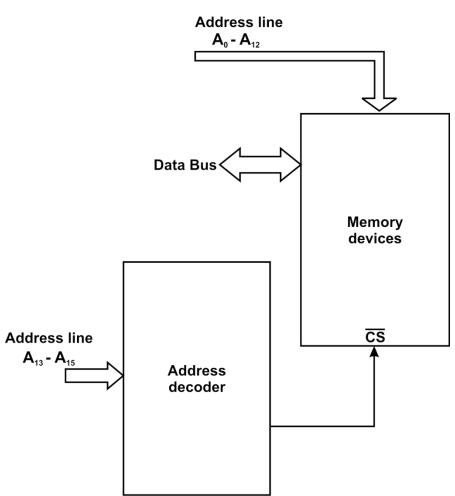

- ➡ In full decoding, all remaining address lines are used for the decoder to generate chip select signal for the memories as shown in figure below:

Fig. 4.9 Full Decoding

- ➡ For example, suppose we want to interface 8k of memory, then thirteen address lines are required for the memory.

- ⇒ Then remaining three address lines can be used for decoder, so more hardware is required for decoding the numbers of address bits.

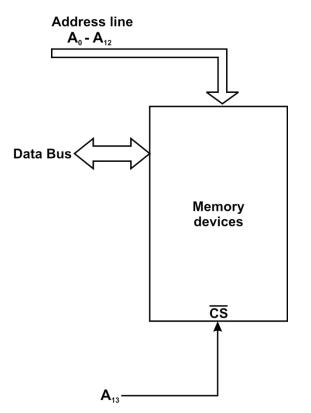

- ⇒ But in partial decoding, only one line out of remaining address lines is used to generate chip select signal as shown in figure below:

## Fig. 4.10 Partial Decoding

⇒ For above example, out of remaining three address lines, we can use any one of them as chip select signal and rest of the address lines will remain open or unconnected, so less hardware is required for decoding.

#### **Difference between Full and Partial Decoding**

| Sr.<br>No. | Full Decoding                                                | Partial Decoding                                                                                                                                                      |

|------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.         | All address lines are used by memory chips and decoders.     | All lines are not used.                                                                                                                                               |

| 2.         | Each memory location has only one unique address.            | Each location has two or<br>more address because the<br>number of addresses per<br>memory location is 2 <sup>n</sup> where<br>n is number of unused<br>address lines. |

| 3.         | Address decoder hardware<br>is complicated and<br>expensive. | Address decoder is simple and less expensive.                                                                                                                         |

| 4.         | The size of memory is not reduced.                           | The size of memory is reduced.                                                                                                                                        |

#### Exercise

- 1. Draw the pin diagram of 8085 microprocessor and explain the various pins.

- 2. Explain the architecture of 8085 microprocessor with the help of the block diagram.

- 3. Explain with the help of a diagram various programmable registers of 8085.

- 4. With the help of a diagram, explain the format of the flag register.

- 5. Explain Program Counter and Stack Register.

- 6. Write a short note on 8085 system bus.

- 7. Explain de multiplexing of address bus of 8085.

- 8. Write a short note on address decoding techniques.

- 9. State the difference between full and partial decoding.

#### References

Computer System Architecture – M. Morris Meno, PHI, 1998

Computer Architecture and Organization - John P Hayes, McGraw Hill, 1998

Digital Computer Fundamentals – Malvino

Digital Computer Fundamentals – Thomas C Bartee, TMG

Computer Organization and Architecture - William Stallings

Microprocessor Architecture and Programming and Applications with the 8085 – R.S. Gaonkar, PRI

# INTERFACING TECHNIQUES

#### **Topics Covered:**

- 5.1 I/O Mapped I/O

- 5.2 Memory Mapped I/O

- 5.3 Difference between Memory Mapped I/O and I/O Mapped I/O

- 5.4 Memory Device

- 5.5 Chip Select Logic

#### Introduction

There are two method of interfacing memory or I/O devices with the microprocessor are as follows:

a) I/O mapped I/O b) Memory mapped I/O

# 5.1 I/O MAPPED I/O

- ⇒ In this technique, I/O device is treated as a I/Q device and memory as memory.

- ⇒ Each I/Q device uses eight address lines.

- ➡ If eight address lines are used to interface to generate the address of the I/O port, then 256 input and 256 output devices can be interfaced with the microprocessor.

- ⇒ The address bus of the 8085 microprocessor is 16 bit, so we can either use lower order address lines i.e.  $A_0 A_7$  or higher order address lines i.e.  $A_8 A_{15}$  to address I/O devices where the address available on  $A_0 A_7$  will be copied on the address lines  $A_8 A_{15}$ .

- ⇒ In I/O mapped I/O, the complete 64 Kbytes of memory can be interfaced as all address lines can be used to address memory locations as the address space is not shared among I/O devices and memory and 256 input and /or output devices.

- ⇒ In this type, the data transfer is possible between accumulator A register and I/O devices only.

- $\Rightarrow$  Address decoding is simple, as less hardware is required.

- ⇒ The separate control signals are used to access I/O devices and memory such as IOR, IOW for I/O port and MEMR,

MEMW for memory hence memory location are protected from the I/O access.

- ⇒ But in this type, arithmetic and logical operation are not possible directly.

- Also we cannot use other register for data transfer between I/O device and microprocessor accepts A register.

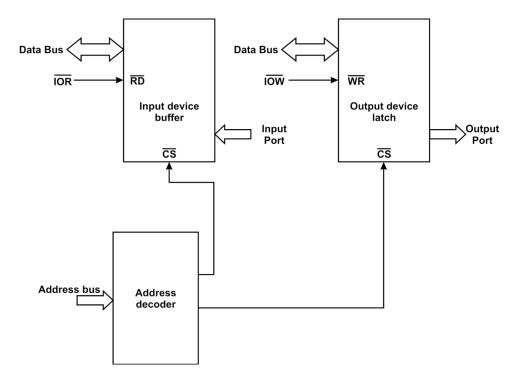

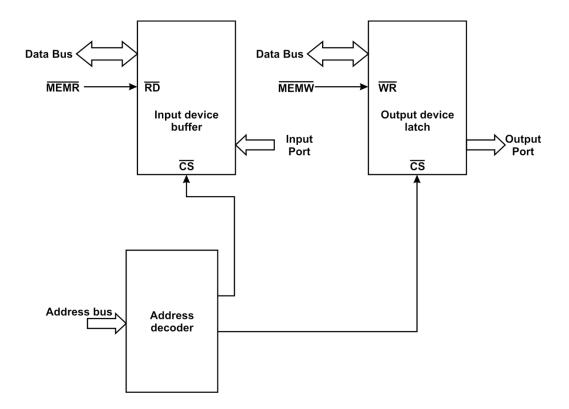

- ⇒ The figure below shows interfacing I/O devices in I/O mapped I/O.

Fig.5.1 I/O mapped I/O ports

### 5.2 MEMORY MAPPED I/O

- ⇒ In this technique, I/O devices are treated as memory and memory as memory, hence the address of the I/O devices are as same as that of memory i.e. 16 bit for 8085 microprocessor.

- So, the address space of the memory i.e. 64 Kbytes will be shared by the I/O devices as well as by memory.

- All 16 address lines i.e. A₀-A₁₅ is used to address memory locations as well as I/O devices. \_\_\_\_\_

- ⇒ The control signals MEMR and MEMW are used to access memory devices as well as I/O devices.

- ⇒ The data transfer is possible between any register of the microprocessor and I/O device or memory device.

- ➡ Hence, all memory related instructions can be used to access devices as they are treated as memory devices.

- Address decoding of the I/O devices and memory devices are complicated and expensive as more hardware is required.

- ⇒ The 8085 microprocessor can access either 64 K I/O ports or memory locations, hence the total numbers of the I/O ports and memory locations should not be greater than 64 K.

- ➡ I/O devices and memory locations are distinguished by the addresses only.

Fig. 5.2 Memory mapped I/O ports

- ⇒ Arithmetic and logical operation can be performed directly on the I/O devices.

- ➡ Most of the memory instructions are long; hence it reduces the speed of I/O.

- ➡ Normally, the speed of the I/O devices are very slow, hence the common interface used in memory mapped I/O will reduce the speed of memory access unnecessarily.

- ⇒ The Figure above shows interfacing of I/O devices in memory mapped I/O.

# 5.3 DIFFERENCE BETWEEN MEMORY MAPPED I/O AND I/O MAPPED I/O

| No       | I/O mapped I/O                                                                                                                      | Memory mapped I/O                                                                                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | I/O devices are treated as<br>I/O devices and memory<br>devices are treated as<br>memory                                            | I/O and memory devices<br>are treated as memory<br>devices.                                                                                                                          |

| 2        | Separate Control Signals for<br>I/O devices are IOR, IOW<br>and memory devices are<br>MEMR, MEMW.                                   | Control signals for<br>memory as well as I/O<br>devices are MEMR and<br>MEMW.                                                                                                        |

| <u>3</u> | IN and OUT instructions are required for I/O read and write operation.                                                              | All memory related instruction are used to Access I/O devices.                                                                                                                       |

| 4        | Data transfer is possible<br>between I/O<br>device and Accumulator only.                                                            | Data transfer is possible<br>between any register and<br>I/O devices.                                                                                                                |

| 5        | Address decoding logic is simple.                                                                                                   | Address decoding logic is complicated and expensive.                                                                                                                                 |

| 6        | 8085 can access complete<br>64 Kbytes of<br>Memory and 256 of Input<br>and 256 output devices as<br>address space is not<br>shared. | 8085 can access 64<br>bytes maximum I/O<br>devices or memory as<br>address space is shared,<br>so total numbers of I/O<br>ports and memory<br>locations should not more<br>than 64K. |

| 7        | I/O Device address is 8 bit<br>and memory address is 16<br>bit.                                                                     | I/O device and memory<br>address is 16 bit as I/O<br>devices are treated as<br>memory.                                                                                               |

| 8        | I/O devices and memory are distinguished by control signals and addresses.                                                          | I/O devices and memory are distinguished by only addresses.                                                                                                                          |

| 9        | Arithmetic and logical operations are not possible directly with I/O devices.                                                       | Arithmetic and logical operations are possible directly with I/O devices.                                                                                                            |

# **5.4 MEMORY DEVICE**